-40%

Lot of 71pcs NCR 86C05 DMA Master Controller IC Chips New

$ 40.53

- Description

- Size Guide

Description

Lot of 71pcsNCR 86C05 DMA Master Controller IC Chips,

8 or 16 Bit DMA interface Supports

Controller,

For Scrap Precious Metal Recovery,or for New Products New Parts,

For Scrap Gold Recovery,

New in Tray

Good Condition IC Chip,Three Trays,

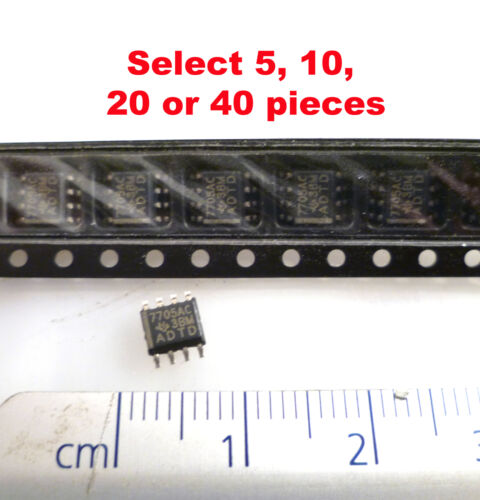

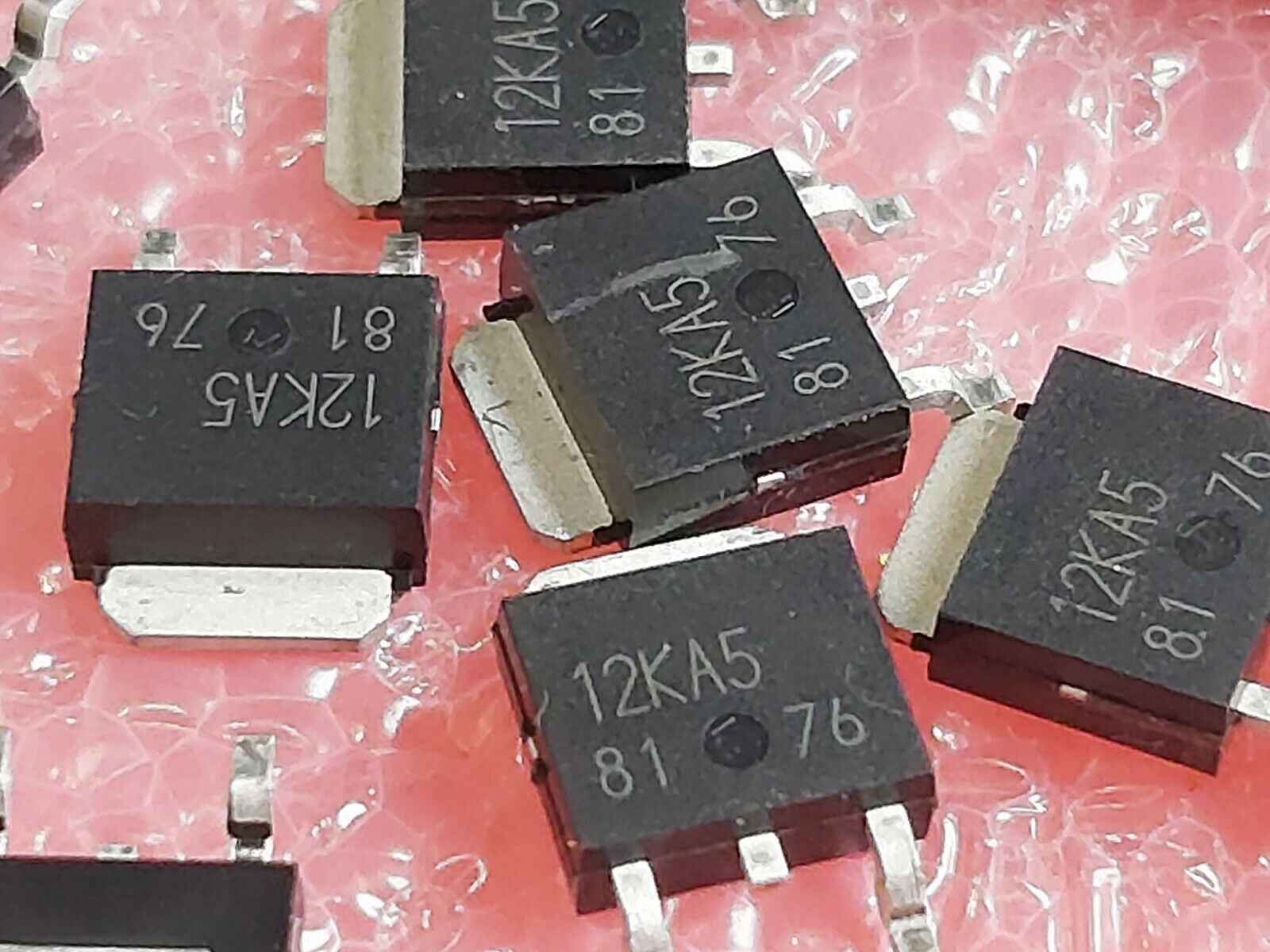

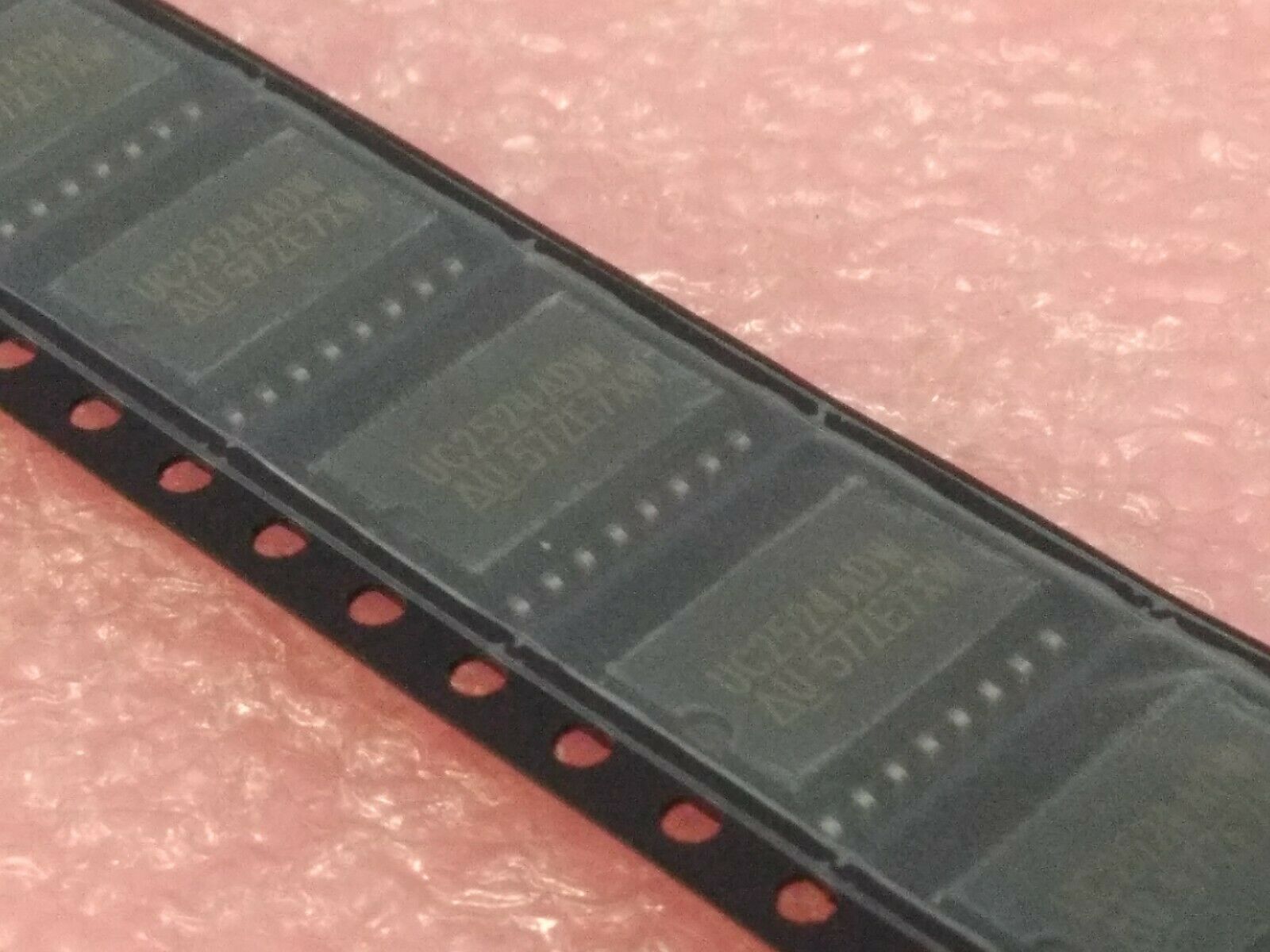

Sold as is(See pictures),

No returns

86C05

Features

•

Connects

to

the

following

host

buses:

1.

IBM

MicroChannel

Bus

2.

IBM

AT

(ISA)

Bus

3.

EISA

Bus

4.

Apple

NuBus

•

Master

mode

host

bus

operation

with

programmable

data

transfer

width

of

8,

16,

or

32

bits

•

Data

transfer

rate

to

20

MBytes/sec

•

Three

independent

host

bus

ports

and

interrupts

to

support

multi-processing

environments.

•

Programmable

host

bus

parameters;

arbitration

level, etc.

• On

chip

32

word

deep

by

32

bit

FIFO

•

Programmable

FIFO

throttle

which

produces

an

extremely high

host

bus

utilization

•

24

bit

host

bus

address

counter

(32

bit

NuB

us)

•

24

bit

transfer

counter

• Six

configuration

registers

• Six

user

defined

host

I/O

registers

•

8 or

16

bit

DMA

interface

supports

DMA

controller

or

DMA

device

operation

•

Programmable

conditions

for

control

microprocessor

interrupt

•

Connects

to

a non-multiplexed

or

multiplexed

(address/data)

control

microprocessor

bus

• BIOS

PROM

support

•

Lock

host

bus

and

set

semaphore

command

•

Clock

rate

to

40

MHz

•

Built

in

host

bus

drivers

for

control

signals

•

Internal

power

on

reset

and

flag

• Single

+5

volt

supply,

CMOS

low

power

consumption

86C05

Features

•

Connects

to

the

following

host

buses:

1.

IBM

MicroChannel

Bus

2.

IBM

AT

(ISA)

Bus

3.

EISA

Bus

4.

Apple

NuBus

•

Master

mode

host

bus

operation

with

programmable

data

transfer

width

of

8,

16,

or

32

bits

•

Data

transfer

rate

to

20

MBytes/sec

•

Three

independent

host

bus

ports

and

interrupts

to

support

multi-processing

environments.

•

Programmable

host

bus

parameters;

arbitration

level, etc.

• On

chip

32

word

deep

by

32

bit

FIFO

•

Programmable

FIFO

throttle

which

produces

an

extremely high

host

bus

utilization

•

24

bit

host

bus

address

counter

(32

bit

NuB

us)

•

24

bit

transfer

counter

• Six

configuration

registers

• Six

user

defined

host

I/O

registers

•

8 or

16

bit

DMA

interface

supports

DMA

controller

or

DMA

device

operation

•

Programmable

conditions

for

control

microprocessor

interrupt

•

Connects

to

a non-multiplexed

or

multiplexed

(address/data)

control

microprocessor

bus

• BIOS

PROM

support

•

Lock

host

bus

and

set

semaphore

command

•

Clock

rate

to

40

MHz

•

Built

in

host

bus

drivers

for

control

signals

•

Internal

power

on

reset

and

flag

• Single

+5

volt

supply,

CMOS

low

power

consumption